Modern digital designs, especially complex System-on-Chip (SoCs), can contain hundreds or even thousands of memory-mapped registers. These registers form the crucial hardware-software interface (HSI), allowing software to configure, control, and monitor the hardware’s operation. For verification engineers, this means that thoroughly testing these registers is a critical, non-negotiable task.

The Universal Verification Methodology (UVM) provides a powerful, standardized framework for this: the Register Abstraction Layer (RAL). RAL creates a high-level model of the registers in your testbench, which makes your code more readable, reusable, and robust. Instead of manually calculating bit shifts and masks, you can access registers by name.

The problem? Manually creating the SystemVerilog code for a UVM register model for a design with thousands of registers is a tedious, time-consuming, and error-prone nightmare. This is a challenge many of us have faced, and it’s a process that can feel overwhelming and frustrating.

Having worked on complex verification environments where design and verification are tightly integrated, I can tell you there’s a better way. In this article, I’ll show you how to automate this entire process using a powerful open-source toolchain called PeakRDL. We will explore how to define registers in a single, human-readable source file and automatically generate the corresponding UVM RAL model, streamlining your verification flow.

Why this matters?

Whether you’re a verification engineer, RTL designer, or firmware developer, register consistency across the project is one of the biggest silent killers of productivity. The techniques in this blog help every team involved: design, verification, and embedded software.

Step 1: Define Your Registers with SystemRDL, the Single Source of Truth

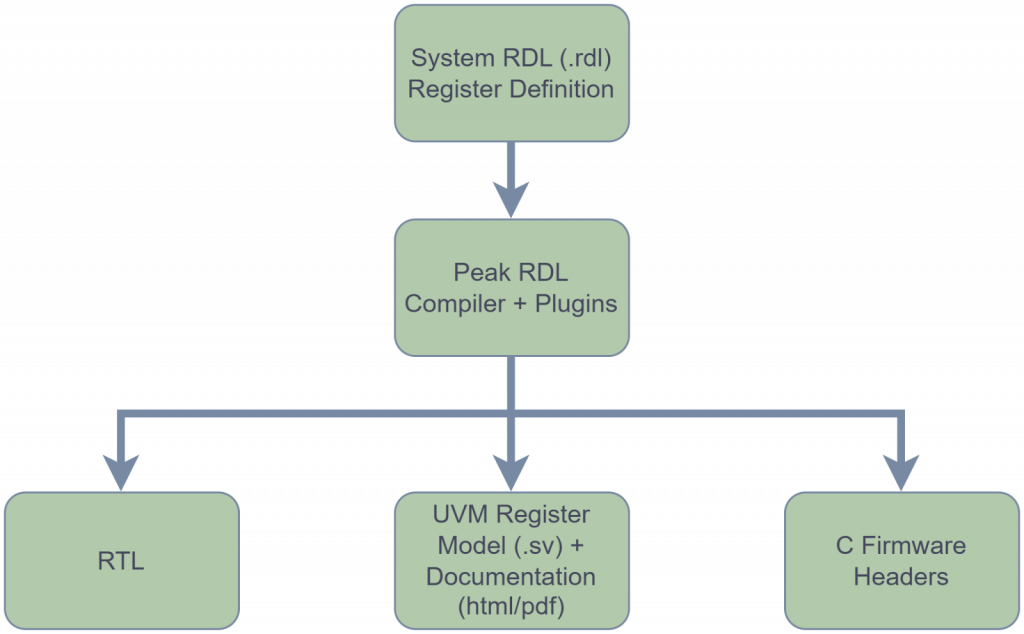

The core idea behind register automation is to have a single source of truth. Instead of having register definitions scattered across spreadsheets, design documents, RTL code, and verification models, you define them once in a machine-readable format. From this one file, you can automatically generate everything you need: RTL, C headers for firmware, documentation, and of course, our UVM RAL model.

While formats like IP-XACT exist, SystemRDL (Register Description Language) is an Accellera standard specifically designed for this purpose. It’s a domain-specific language that is both human-friendly and powerful enough to capture complex register behaviors.

In real SoCs we usually deal with more complex patterns: register arrays, interrupt maps, indirect addressing, shadow registers, or hardware-updated status fields. SystemRDL handles all of these cleanly, and PeakRDL translates them into UVM code automatically.

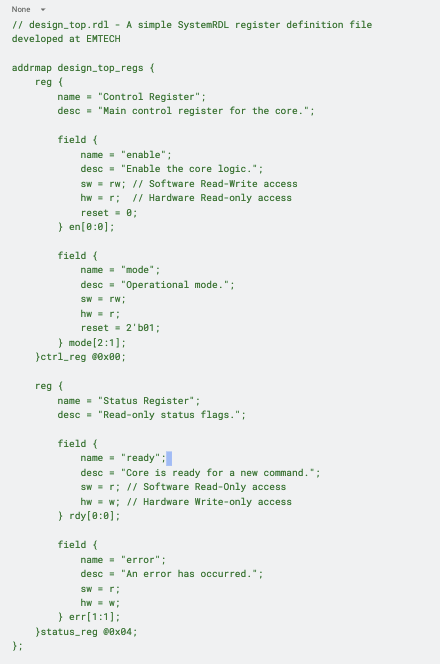

For this example developed at EMTECH, we will use a simple SystemRDL file named design_top.rdl. This file defines the register map for a small block, including registers, fields, addresses, access policies (like Read-Write or Read-Only), and reset values.

This simple text file is now our golden source for the register specification. Any change here can be automatically propagated to all other project’s areas, ensuring consistency and dramatically reducing bugs.

Step 2: Introducing PeakRDL – Your Automation Toolchain

Now that we have our register specification, we need a tool to process it. PeakRDL is an open-source toolchain built around a SystemRDL compiler. It’s designed to be accessible and highly extensible through a plugin-based architecture.

PeakRDL can take our .rdl file and generate various outputs, called “exporters”. There are official exporters for:

- Synthesizable RTL (SystemVerilog)

- Interactive HTML Documentation

- C Header Files for firmware development

- UVM Register Models

This is exactly what we need to automate our verification flow.

Step 3: Generate the UVM RAL Model with a Single Command

With PeakRDL installed, generating the UVM RAL package is incredibly straightforward. In the EMTECH project referenced earlier, this step was automated through a generate.sh script. The script invoked PeakRDL to process the SystemRDL file (design_top.rdl) and produce the corresponding UVM package (design_top_ral_pkg.sv), which contains the auto-generated register model classes, such as the top-level block design_top_regs_block and all underlying uvm_reg and uvm_reg_field objects.

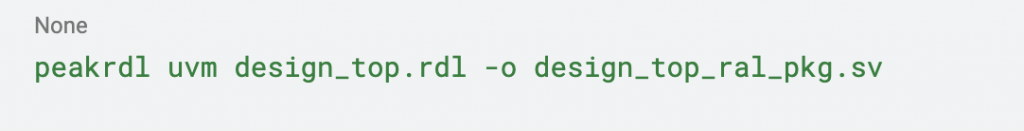

Here’s how you can do it directly from the command line:

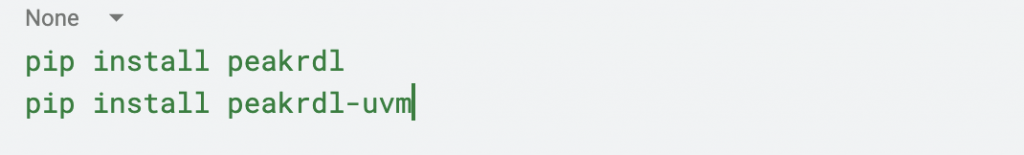

1. Install PeakRDL and the UVM exporter plugin:

2. Run the generator:

3. This single command reads our design_top.rdl file, compiles it, and uses the uvm exporter to generate a complete UVM RAL model in design_top_ral_pkg.sv.

The generated file will contain all the necessary UVM classes (uvm_reg_field, uvm_reg, uvm_reg_block) that perfectly mirror the structure we defined in SystemRDL. It includes the build() method, address maps, and hierarchical paths needed for both frontdoor (bus-based) and backdoor (direct RTL) access.

To better visualize how everything connects, the diagram below shows how SystemRDL and PeakRDL work together to produce all the artifacts needed by design, verification, and firmware teams.

Step 4: Integrate the Generated Model into Your Verification Environment

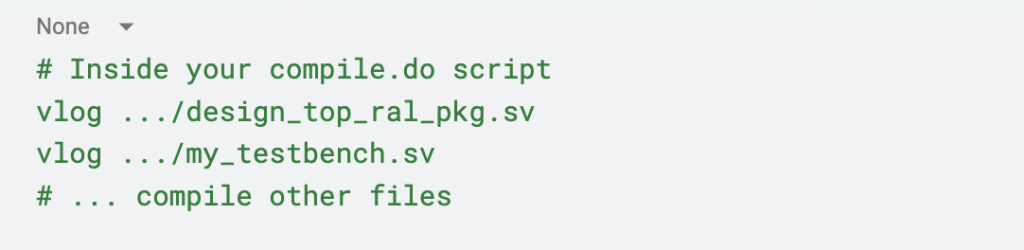

The final step is to integrate this auto-generated package into your UVM testbench. In the EMTECH project, this was handled by a compile.do script, which is part of a larger, make-driven flow.

Here’s a simplified breakdown of the integration process:

1. Compile the generated package: Your simulator’s compile script (e.g., a compile.do file for QuestaSim) needs to compile the design_top_ral_pkg.sv file along with your other UVM components like agents, sequences, and the testbench top.

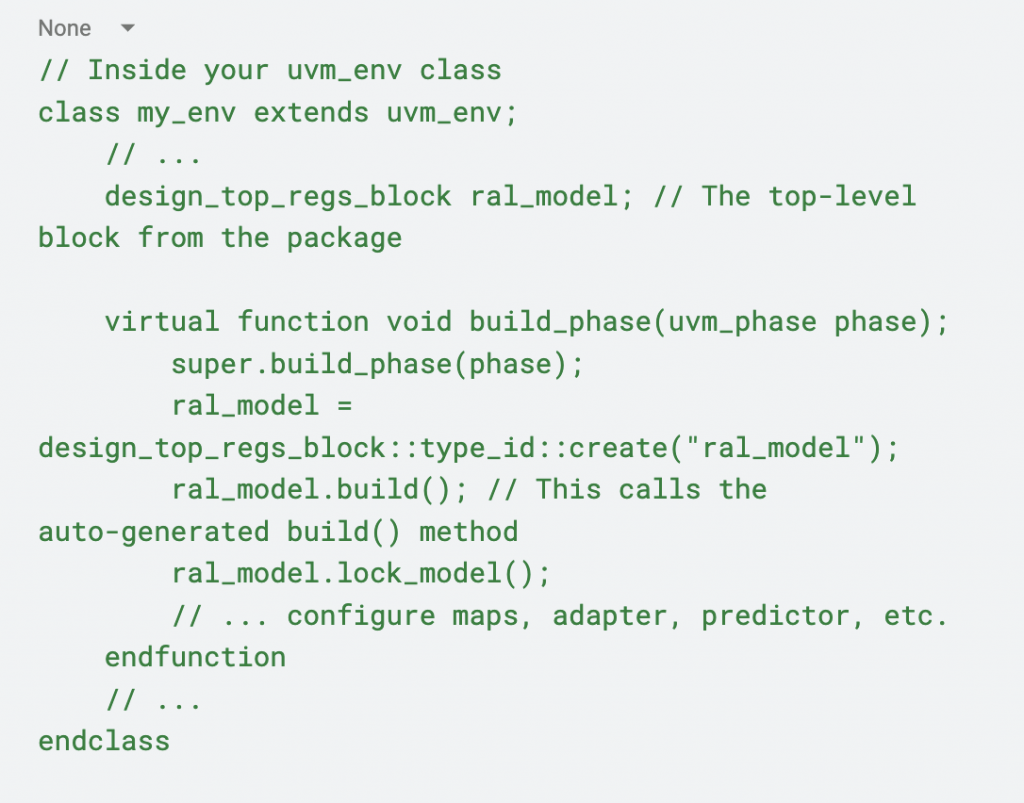

2. Instantiate and build the model: In your UVM environment (typically in the build_phase), instantiate the generated register block.

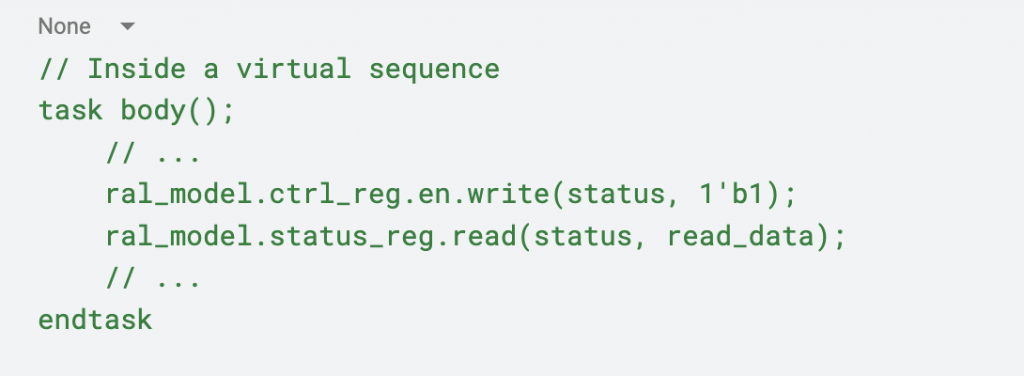

3. Use the model in your sequences: Now, your UVM sequences can access registers by name, using abstract methods like write() and read(), without needing to know the physical addresses.

This approach creates an efficient and scalable cycle between RTL design and functional verification. By leveraging tools like PeakRDL, you connect a robust simulation environment like QuestaSim with your design specifications, achieving faster and more reusable verification.

Conclusion: Embrace Automation for a Better Workflow

Manually managing registers is a relic of the past. By adopting a single-source-of-truth methodology with SystemRDL and an automation toolchain like PeakRDL, you can eliminate a significant source of bugs, save countless hours of tedious work, and keep your design, verification, and documentation perfectly in sync.

This automated flow, as implemented in real-world projects, demonstrates how modern open-source tools can dramatically improve efficiency. The UVM Register Model is a powerful feature, and with tools like PeakRDL, leveraging it has never been easier. So, stop hand-coding your register files and let automation amplify your influence and productivity.

Bibliography

- Agnisys. (2024, January 12). Deep Dive into UVM Register Model. https://www.agnisys.com/blog/deep-dive-into-uvm-register-model/

- Mykyta, A. (2023, April 29). PeakRDL: An accessible and extensible SystemRDL CSR automation toolchain [Video]. YouTube.https://www.youtube.com/watch?v=ag9TaeeWlzs

Written by Patricio Gallo

Edited by Adrián Evaraldo

For further inquiries, contact us: info@emtech.com.ar